#include <fltperiphregister.h>

Public Member Functions

- FltPeriphRegister (const char *name, int slotID, int regID, int r, int w, int len)

- int getFpgaNr (int pixel)

- int getInternalNr (int pixel)

- int getPixelNr (int fpgaNr, int internal=0)

- unsigned long getPixelMask (unsigned long *internalMask)

- void getInternalMask (unsigned long pixelMask, unsigned long *internalMask)

- unsigned long read (int fpgaNr)

- void read (unsigned long *data)

- void write (int fpgaNr, unsigned long data)

- void write (unsigned long *data)

- void writeBits (int fpgaNr, unsigned long data, unsigned long mask, int shift)

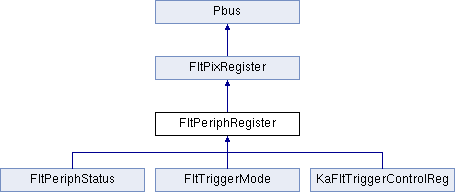

Detailed Description

The Flt board contains four pheripheral FPGAs.

The status of each FGPA is set by a register. The four peripherial FPGA registers are addressed via the channel address. The relation between FGGA nr (1..4) and channel address (0..31) is channel address = (nr<3)? nr-1: nr+9. The read and write methods have been redefined to allow the usage of the fpga number. The broadcast is valid as implemented in FltPixRegister.

Each FPGA is responsible for 6 pixel in the column. These 6 pixel are also called channels (1..6).

Relation between Pixel and FPGAs (Channels are numbered from the left to the right):

* 1 2 * pixel 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 * fpga 1 x x x x x x * 2 x x x x x x * 3 x x x x x x * 4 x x x x x x *

Changes:

- Error in the calculation of the corresponding pixel number for the fpgas.

- Todo:

- It may be more consistent to number the FPGAs also starting with 0 ?!

- Todo:

- There are inconsistencies in the definition of the relation between pixel number and fpga number?!

Definition at line 58 of file fltperiphregister.h.

Constructor & Destructor Documentation

| FltPeriphRegister::FltPeriphRegister | ( | const char * | name, |

| int | slotID, | ||

| int | regID, | ||

| int | r, | ||

| int | w, | ||

| int | len | ||

| ) |

Member Function Documentation

| int FltPeriphRegister::getFpgaNr | ( | int | pixel | ) |

Return the number of the FPGA for a certain pixel.

| void FltPeriphRegister::getInternalMask | ( | unsigned long | pixelMask, |

| unsigned long * | internalMask | ||

| ) |

Re-oder the pixel in the external pixel mask to the internal oder.

| int FltPeriphRegister::getInternalNr | ( | int | pixel | ) |

Return the internal channel number (0...5) in the fpga.

| unsigned long FltPeriphRegister::getPixelMask | ( | unsigned long * | internalMask | ) |

Re-oder the pixel in the internal masks to the order given by the external pixel number.

For the internal mask a array of length 4 has to be provided.

| int FltPeriphRegister::getPixelNr | ( | int | fpgaNr, |

| int | internal = 0 |

||

| ) |

Return the number of one pixel (0..23) for a certain fpga.

| unsigned long FltPeriphRegister::read | ( | int | fpgaNr | ) |

Redefinition to map the fpgaNr to the proper channel address.

Reimplemented from FltPixRegister.

| void FltPeriphRegister::read | ( | unsigned long * | data | ) |

As there is only PBUS single access allowed, this methods emulates the block wise access.

| void FltPeriphRegister::write | ( | int | fpgaNr, |

| unsigned long | data | ||

| ) |

Redefinition to map the fpgaNr to the proper channel address.

Reimplemented from FltPixRegister.

| void FltPeriphRegister::write | ( | unsigned long * | data | ) |

As there is only PBUS single access allowed, this methods emulates the block wise access.

Reimplemented from FltPixRegister.

| void FltPeriphRegister::writeBits | ( | int | fpgaNr, |

| unsigned long | data, | ||

| unsigned long | mask, | ||

| int | shift | ||

| ) |

Redefinition to map the fpgaNr to the proper channel address.

Reimplemented from FltPixRegister.

The documentation for this class was generated from the following file:

- /home/kopmann/git-mirror/fdhwlib/fdhwlib/Hw/fltperiphregister.h