#include <basefifo.h>

Public Member Functions

- BaseFIFO (const char *name, int slotID, unsigned int regID, int r, int w, int len=1, int addrShift=0, int blockLen=1, bool useCache=false)

- virtual void readBlock (unsigned long *data)

- virtual void readBlock (unsigned long *data, unsigned long blockLen)

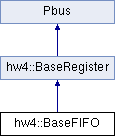

Detailed Description

The class contains the register address modell of the SLT board.

The individual register address is calculated from the slot ID and the register ID.

The register implementation contains a cache function to avoid unneccessary access to the hardware. To decode the status bits the cache content can be used without storing any additional intermediate data.

Definition at line 32 of file basefifo.h.

Constructor & Destructor Documentation

| hw4::BaseFIFO::BaseFIFO | ( | const char * | name, |

| int | slotID, | ||

| unsigned int | regID, | ||

| int | r, | ||

| int | w, | ||

| int | len = 1, |

||

| int | addrShift = 0, |

||

| int | blockLen = 1, |

||

| bool | useCache = false |

||

| ) |

A register (slt object) is defined by it's name and the combination of slot ID and register ID.

Every register also posses the properties readable and writeable. The register object can also be used to access register vectors and memories. For a register vector the number of elements and the address shift needs to be specified. A memory also needs both parameters. Memories span a contiouous space so that block access can be used to get the data for all elements.

A FIFO does not provide random access to the data. It needs to read all data from the same address. In Pbus the increment option is used to leave out any modification of the base address.

Member Function Documentation

| virtual void hw4::BaseFIFO::readBlock | ( | unsigned long * | data | ) | [virtual] |

Read all elements of the register vector return the data and store it in the object cache.

Reimplemented from hw4::BaseRegister.

| virtual void hw4::BaseFIFO::readBlock | ( | unsigned long * | data, |

| unsigned long | blockLen | ||

| ) | [virtual] |

Read all elements of the register vector return the data and store it in the object cache.

Reimplemented from hw4::BaseRegister.

The documentation for this class was generated from the following file:

- /home/kopmann/git-mirror/fdhwlib/fdhwlib/hw4/basefifo.h